Email: editorijerst@gmail.com or editor@ijerst.com

ISSN 2319-5991 www.ijerst.com Special Issue, Vol. 1, No. 1, March 2015 National Conference on "Recent Prends in Communication & Information Technologies" NCRTCIT 2015 © 2015 IJERST. All Rights Reserved

Research Paper

# OPTIMAL REPAIR RATE AND AREA REDUCTION FOR EMBEDDED MEMORIES BY USING BIRA & AMT

V Geetha<sup>1\*</sup>, X Susan Christina<sup>1</sup> and X Susan Christina<sup>1</sup>

\*Corresponding Author: V Geetha ⊠ geeta93selvi@gmail.com

As the capacity and density of embedded memories have rapidly increased, the probability of memory faults will increase. That results in yield drops and quality degradation. Yield improvement of embedded memories have become very important. Yield refers to the percentage of good die on the wafer. For embedded memories Built-In-Redundancy-Analysis (BIRA) is used to achieve optimal repair rate and yield improvement. In this Project the proposed scheme generates set of test patterns with weights 0, 0.5 and 1 using an accumulator-based-3 weighttest pattern generation. In a Built-In Redundant analysis (BIRA) scheme, it performs exhaustive search to find and repair the faults in RAM. It uses part of spare memory as an AMT(Address Mapping Table) to reduce the faulty cell address to its logical address which consumes less area. And by using tiling technique in spare memory permanent faults were handled. These reduced addresses are stored in CAM (Content Addressable Memory) which is used during the Redundant Analysis procedure.

Keywords: Addressable Memory (CAM), Built in redundancy analysis (BIRA), Built in self test (BIST), Accumulator based 3-weighted test pattern generation.

### INTRODUCTION

In modern system-on-chip (SOC) designs, embedded memories occupy a significant portion of the chiparea. Embedded memory plays a vital role in manyelectronic devices such as set-top boxes, sensors, industrialmeters and mobile phones due to its small size. Embeddedmemory mainly focuses on the reliability rather than largesize, so it is tested for faults using BIST.As the capacity anddensity of semiconductor memories have rapidly increasedwith the

technological development of semiconductor manufacturing, the probability of memory faults has increased. This causes yield drops and quality degradation..As the chip area increases yield is reduced. In order toimprove the yield, testing is done by the embedded system. Circuit manufacturer must thoroughly test their products before delivering them to the customers. Built-inRedundancy-repair (BISR) techniques are one main yieldenhancementtechnique for embedded RAMs with redundancy.

<sup>&</sup>lt;sup>1</sup> M.I.E.T Engineering College, Trichy, Tamilnadu, India

Embedded memory is tested by using a builtin self-test(BIST) module or external automatic test equipment (ATE)before RA is performed. According to the testing method, there are two methods to repair faulty memories. They are BIRA module and an external ATE. Most RA algorithms have been based on 2-D redundantcells since the 1980s. Furthermore, various RA algorithmsfor 2-D redundancy have been developed. They are Repairmost(RM), CRESTA, LRM, and ESP are the most wellknownRA algorithms for built-in redundancy analysis(BIRA).RM(Repair most) is a simple algorithm. It counts the number of faults in each line and allocates the spare linesto a faulty line in descending order of the number of faults. Although its repair rate is high, it is not optimal, because anexhaustive search is not performed. CRESTA (Comprehensive Real-time Exhaustive SearchTest and Analysis) focuses on the optimal repair rate and fast analysis. But the hardware cost is high. LRM (Linear Repair Most)and ESP(Essential Spare Pivot) mainly focuson minimizing the area overhead in terms of storagerequirements with a simple RA algorithm. However, therepair rates of the two algorithms are not optimal sincefaulty information is omitted. IS (Intelligent Solve) and ISF (Intelligent Solve First) algorithms achieve both low areaoverhead and an optimal repair rate. However, the two algorithms take a lot of time to complete the RA in caseswith complex fault distributions.

Recently, many tree-based RA algorithms have also been introduced that make an effort to lessen the search space. These algorithms are based on the branch and bound (B&B) algorithm. The B&B algorithm is a simple fault-driven approach. To overcome the restriction of these approaches, SFCC and BRANCH analyzer were

introduced.SFCC(Selected fault count comparison) achieves a low areaoverhead and optimal repair rate, and reduces the searchspace by building a search tree based on the line faults.BRANCH analyzer analyzes all nodes concurrently within abranch for combinations of 2-D spares. In order to analyzeall nodes concurrently and achieve an optimal repair rate, BRANCH analyzer and SFCC store all fault informationinto fault-storing content-addressable memories(CAMs). Most BIRA approaches require extra hardwareoverhead in order to store and analyze faults in the memory. Existing approaches do not utilize spare memories duringthe redundancy analysis procedure. Proposed system uses part of the spare memory as anAddress Mapping Table (AMT) in order to reduce the areaoverhead created by Built-In Redundancy Analysis (BIRA)scheme.

#### RELATED WORK

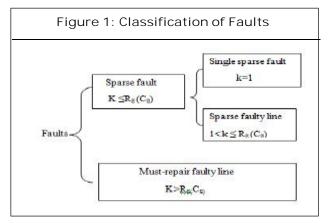

#### A. Fault Classification

A fault in a system is some deviation from the expected behaviour of the system: a malfunction. Faults inembedded memory may be due to variety of factors, including hardware failure, operator (user) error. Faults can be classified into one of three categories:

#### **Transient Faults**

These occur once and then disappear. For example, anetwork message doesn't reach its destination but does whenthe message is retransmitted.

#### Intermittent faults

Intermittent faults are characterized by a fault occurring, then vanishing again, then reoccurring, then vanishing. These can be the most annoying

of component faults. Aloose connection is an example of this kind of fault.

#### **Permanent Faults**

This type of failure is continues to exist until the faultycomponent is repaired or replaced. Examples of this fault aredisk head crashes, software bugs, and burnt-out powersupplies.

The **failure pattern** is classified into six types: word linefault, bit line fault, cluster fault, continuous fault, twin fault, and single fault. Word (bit) line fault is column (row)failures. Cluster fault is formed of various shapes by distribution of faulty cells. Continuous fault is a line fault which has greater than two faults, i.e., faulty cells are continuously distributed. Twin fault is formed by a line faultor a diagonal fault by two faults. A single fault does not share a row and column address with other faults. Since a memory with 2-D spare architecture is repaired by line replacement, faults (failure pattern) were classified into three types:

- · single fault

- · sparse line fault,

- must-repair line fault.

Diagonal fault of twin fault and single fault can be defined as a single fault. Sparse line fault is a faulty row or column line. The number of spare rows and columns are Rs and Cs, respectively A faulty row (column) line has more than one and less than or equal to Cs (Rs) faults. Cluster fault, continuous fault, and line fault of twin fault can be defined as a sparse line fault. A must-repair faulty row (column) line has greater than Cs (Rs) faults. Word line fault, bit line fault, part of cluster fault, and continuous fault can be defined asmust-repair line fault. Because the cluster faults containmany cross line faults, the cross line faults generate complicated cases for RA.

## **B. Spare Memory**

Spare memory is a division of memory. Embeddedmemory is divided into two channels. The first channel ismirrored to the second channel, creating a redundant copy ofmemory. If a fault occurs within the memory of one channel, the memory controller shifts to the paired channel without disruption, and the channels can re-synchronize when repairs are completed. In sparing mode, the trigger for failover is apreset threshold; when the threshold is reached, the content is copied to its spare counterpart and it is activated for use.

## C. Content Addressable Memory

CAM is designed to search its entire memory in asingle clock cycle, it is much faster than RAM in virtuallyall search applications. CAMs are widely used wherever fastparallel search operations are required. CAM is a storagearray designed to find the location of a particular storedvalue. The main difference between a Content Addressable Memory and a Random Access Memory (RAM) is that, in aRAM the user supplies the address and gets back the data and gets back theaddress. In BIRA the cam can be used to store the

reducedaddresses given by AMT for analyzing the fault addressusing RA procedure.

# Redundancy Analysis (RA)

After the fault collection, Redundancy Analysis(RA) procedure is done by the embedded system to findrepair solutions. In order to achieve an optimal repair rate, an RA algorithm, which is an exhaustive search method, isused. Optimal repair rate is the rate of occurrence of failureincidences for a repairable system. It is defined as the ratioof memories repaired by redundancy analysis to all repairable of the total tested memories.

Optimal repair rate =

Memories repaired by BIRA

All repairable memories of the total tested memories

During Redundancy Analysis, all the solutioncandidates are applied to the faults according to the number of faults. If there is one solution at least, then the memory isrepairable. If there is no solution after all the solutioncandidates are applied to the faults, then the memory isirreparable. If the number of faults is less than the sum of theavailable spare memories, there may be no solution by applying solution candidates to the row and columncombinations of the faults.

#### PROPOSED WORK

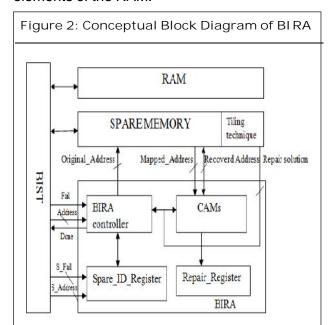

The conceptual block diagram of a built-inredundancy analysis (BIRA)is shown below, which iscomposed of BIST and BIRA. Here the spare memory isused as an AMT, so it is tested by BIST before the RAM istested. This BIRA scheme has two modes, 1) Test mode 2)Normal mode.

In the test mode, BIST detects the faults in the RAM and sends the fault information to BIRA.

BIRA canthen change the fault addresses into short mapped logicaladdresses. The BIST tests the RAM and the BIRAdetermines the redundancy allocation for efficientlyreplacing the defective elements of the RAM.

The proposed BIRA consists of BIRA\_Controller, fault storing CAMs, Spare\_ID\_ register, and Repair\_register. The controller performs several procedures: it compares faulty addresses, stores the original addresses in the AMT, stores the mapped addresses in the CAMs, and recovers the mapped addresses to the original addresses.

The mapped addresses are stored in the fault storingCAMs. The faulty addresses of the faulty spare memories are stored in the Spare\_ID\_register. The faulty spare memory is not suitable to use for the AMT as also to replace faulty memory lines. and by using the tiling technique in the spare memory the permanent faults are handled. If detect any permanent faults in memory the testing control avoid the prohibited zone to apply the processes it will avoids usage of the faulty zone. It will reduce the processing time and

increases the processing speed. That is, BIRA schemes perform RA procedures takinginto account the amount of remaining good spare memory. The repair registers store the repair solutions, which are thememory addresses from the BIRA controller. Once the RAprocedure is completed, the spare memories are allocated according to the information in the Repair register.

The spare memory is tested before the RAM is tested. Because the RAM cannot be repaired by a faulty spare memory and we do not use the faulty spare memory as anAMT, the address of faulty spare memory should be storedin the Spare\_ID\_register. When BIST detects a fault from the spare memory, the signal S\_Fail is asserted, and the faulty addresses are sent to the Spare\_ID\_register through the port S\_Address. The BIRA\_Controller counts the available spare memories and checks faulty spare memory toperform an adequate RA procedure.

After the test for the spare memory is done, the RAM istested. When BIST detects a fault, it pauses and the signalFail is asserted. The faulty addresses are then sent to BIRAthrough the port Address. If the fault is the first one, theBIRA\_Controller stores the fault address to the AMT byavoiding faulty spare memory in the Spare\_ID\_register. Otherwise, the BIRA\_Controller compares the addresses with already stored addresses in the AMT through the portOriginal\_Address.

If the address is the same, its mapped addresses are sent to the BIRA\_Controller through the portMapped\_Addressand are stored in the CAMs. Otherwise, the address is stored in the AMT and mapped to short logical addresses. Thesemapped addresses are sent to the BIRA\_Controller through the port Mapped\_

Address and stored in the CAMs. Once themapped addresses are stored in the CAMs, theBIRA\_Controller asserts the signal Done, and BISTcontinues the test.

After the test is completed, BIRA finds the repair solutionby analyzing the fault information of the CAMs using the proposed RA algorithm. Because the repair solutions are composed of the mapped addresses, they are recovered to the original addresses through port Recover\_Address. Finally, the repair solutions, which are composed of theoriginal addresses, are stored in the Repair\_register through the port Repair\_Solution to replace the faulty lines of RAMwith spare memories.

Proposed BIRA uses the Content Addressable Memoryto store the logical address of the faulty cells in RAMmemory. When a fault is detected during the BISTprocedure, the BIRA controller stops the testing and storesthe corresponding faulty cell address in the spare memoryand it is mapped to logical address. This logical address isthen stored in CAM. When CAM receives an input faultyaddress, it searches the already stored data for match. If theincoming address is not available in its stored data, then itstores the faulty incoming address. This CAM content is used during the repairing procedure in order to recover theoriginal address.

# SIMULATION RESULTS

Spare memory is tested before RAM, becausefaulty spare cells cannot be used as Address Mapping Table.Input\_address and the s\_address are the inputs. Theinput\_address and the spare cell address i.e. s\_address arecompared in order to find the Address non-uniqueness typefault. If two addresses are same then it is considered as faultbecause, two cells

Figure 3: Simulation Result for Fault Detection in Sparememory

have same address i.e. address is not aunique one and it is declared as fault. Whenever a faultoccurs, the s\_fail signal is asserted and the correspondingfaulty address is stored in spare\_id\_register. Number ofspare faults is counted by the variable count.

Figure 4: Simulation Result for BIRA Scheme

# FURTHER IMPLEMENTATION

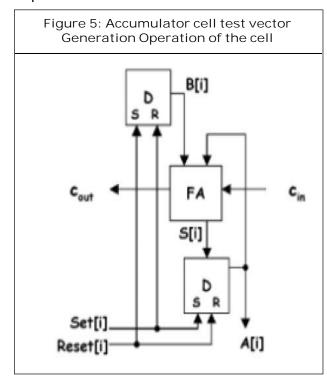

BIST is a design-for-testability technique thatplaces the testing functions physically with the circuit undertest (CUT). The basic BIST architecture requires the additionof three hardware blocks to a digital circuit: a test patterngenerator, a response analyzer, and a test controller. The testpattern generator generates the test patterns for the CUT. Anaccumulatorbased 3-weight test pattern generation schemegenerates set of patterns with weights 0, 0.5, and 1. Sinceaccumulators are commonly found in current VLSI chips, this scheme can be efficiently utilized to drive down thehardware of built in self test pattern generation, as well. The implementation of the 3-weighted-test patterngeneration scheme is based on the full adder. Therefore, inorder to transfer the carry input to the carry output. The logicmodule provides the Set and Reset signals that drive the Sand R inputs of the Register A and Register B in-puts.

- I. For A[i] =1 , We give set[i]=1 and reset[i]=0 and henceA[i]=1 and B[i]=0. Then the output is equal to 1, and Cin will be equal to Co. Cin is transferred to theCout.

- II. For A[i] =0 , We give set[i]=0 and reset[i]=1 and henceA[i]=0 and B[i]=1. Then the output is equal to 0, and here Cin is equal to Cout. Cin is transferred to theCout.

- III. For A[i] = "-", set[i] =0 and reset[i] =0. The D input of the flip-flop of register B is driven by either 1 or 0, depending on the value that will be added to the accumulator inputs inorder to generate satisfactorily random patterns to the inputs of the CUT.

The signals that drive the S inputs of the flip-flops of Register A, also drive the R inputs of the flip-flops of Register B and vice versa. The implementation of the proposed weighted pattern generation scheme is based on the accumulator cell is given in Figure 1, which consists of a Full Adder (FA) cell and a D-type flip-flop with a synchronous set and reset inputs whose output is also driven to one of the full adder inputs. This technique is used without loss of generality, that the set and reset are active high signals. The respective cell of the driving register B[i]is also shown.

# CONCLUSION

A Built-in Redundancy Analysis scheme for embeddedmemories is proposed. Fault collection in spare memoryfollowed by RAM, address mapping and repair analysis aresome of the steps in BIRA. Faults due to address nonuniquenessare considered here and fault addresses are collected using BIRA controller. Collected faulty addresses are mapped using Address Mapping Table which resides inspare memory. Mapped

faulty addresses are stored finally inContent Addressable Memory. And by using the tillingtechnique in spare memory permanent faults were handled. If detect any permanent faults in memory the testing controlavoid to apply the process to that zone. So It will reduce the processing time so speed will increases. An accumulator based 3 weighted test pattern generation will used forgenerating test sequence. It can be implemented using anyadder design and then it does not require any modification of the adder; hence it does not affect the operating speed of the adder. By comparing existing system this proposed system is advanced for embedded memories.

#### REFERENCES

- Chang D.M. Li J.F. and Tseng T.-Wand(2006), "A builtinredundancy-analysis scheme for RAMs with 2-Dredundancy using 1-D local bitmap," in Proc. Design, Autom. Test Eur., pp. 53–58, Mar.

- Cho H. and Kang W. et.al(2010), "A built-in redundancyanalysis with a minimized binary search tree," ETRI J., vol.32, no. 4, pp. 638– 641, Aug.

- Chen T.-J. and Li J.-F. et.al(2012), "Costefficient built-inredundancy analysis with optimal repair rate for RAMs," IEEE Trans. Comput. - Aided Design Integr. Circuits Syst., vol. 31, no. 6, pp. 930–940, Jun.

- Han.T,W. and Jeong et.al(2010), "An advanced BIRA formemories with an optimal repair rate and fast analysis speedusing a branch analyzer," *IEEE Trans. Comput.-AidedDDesign integr, vol 29, no 12*, pp. 2014-2026, Dec.

- 5. Jeong W., Jin and Kang I. et.al(2009), "A Fast

- Built-inRedundancy Analysis for Memories With Optimal RepairRate Using a Line-Based Search Tree",IEEE Trans VeryLarge Scale Inter (VLSI) Systems.,vol 17,no 12,pp.1665-1678,Dec.

- 6. Jeong W., Kang I., Jin K. and Kang S. (2009), "A fastbuilt-in redundancy analysis for memories with optimalrepair rate using a line-based search tree," IEEE Trans. VeryLarge Scale Integr. (VLSI) Syst., vol. 17, no. 12, pp. 1665–1678, Dec.

- Joohwan Lee, Kihyun Park and Sungho Kang(2012), "High-efficiency BIRA for embedded memories with a highrepair rate and low area overhead"., Journal ofsemiconductor technology and science, vol.12, no.3, pp.515–517, sep.

- 8. Lee J., Park K. et.al(2009), "An area-efficient built-inredundancy analysis for embedded memories with optimal repair rate using 2-

- D redundancy," in Proc. Int. SoC DesignConf., , pp. 353–356, Nov.

- Li J.-F,Tseng T.W. et.al(2010), "ReBISR: AReconfigurable Built-In Self-Repair Scheme for RandomAccess Memories in SOCs" ", IEEE Trans Very Large ScaleInter (VLSI) Systems., vol 18, no 6, pp. 921-937, Jun.

- Pagiamtzis.K and Sheikholeslami A.(2006), "Contentaddressablememory (CAM) circuits and architecture: Atutorial and survey," IEEE J. Solid-State Circuits, vol. 41,no. 3, pp. 712–727, May.

- 11. Wooheon Kang, Hyungjun Cho, Joohwan Lee, andSungho Kang, Member, IEEE., "A BIRA for MemoriesWith an Optimal Repair Rate Using Spare Memories forArea Reduction"., IEEE transactions on very large scaleintegration (vlsi) systems, vol. 22 pp. 2336-2349 October2013

International Journal of Engineering Research and Science & Technology

Hyderabad, INDIA. Ph: +91-09441351700, 09059645577

E-mail: editorijlerst@gmail.com or editor@ijerst.com

Website: www.ijerst.com